Mr. Smithとインピーダンスマッチングの話

【第18話】 S12の正体

第17話ではトランジスタ増幅器の入出力インピーダンスが、何故相手ポートの影響を受けるのかと、これを考慮した整合回路設計を行う方法をご説明しました。一方で世の中の教科書や、専門書では、トランジスタの入出力整合回路を設計する時に、トランジスタの入出力インピーダンスをS11、S22として設計する手法が多く書かれています。今月はこのあたりを中心にお話させて頂きます。

1. 理想の増幅器

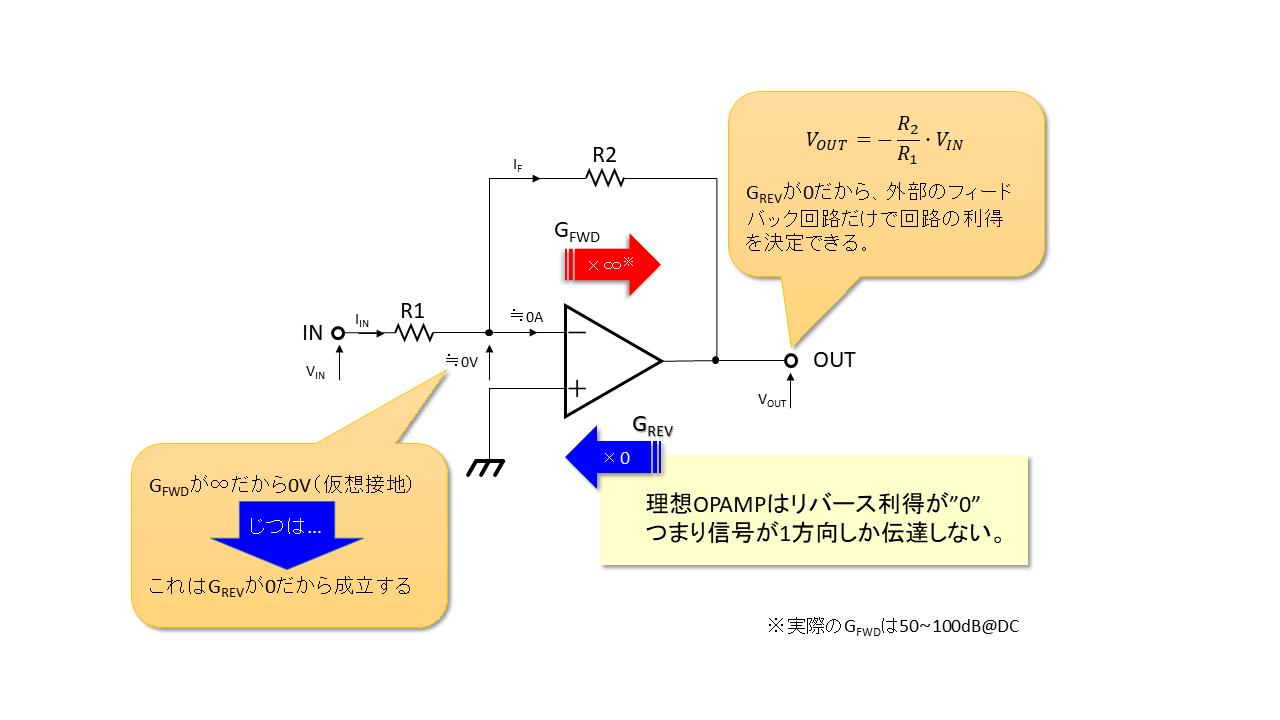

第17話においてS12≒0だったら、S11は負荷抵抗の影響を受けないし、S22は信号源抵抗の影響を受けないと申し上げました。オペアンプの特性を思い出して頂きたいのですが、理想の増幅器は順方向に大きな+の利得があって、逆方向には信号が通らない(大きな-の利得がある、または0)です。そうしないと増幅器の内部で信号がフィードバックしてしまい、動作が不安定になります。図1に示すようにオペアンプは理想増幅器に近い特性を有していて、回路設計の際に逆方向の利得を考える事はまずありません。故に外部のフィードバック抵抗だけで利得を決めることができるのです。

2. S12の正体

つまりS12というのは逆方向の伝達利得ですから、トランジスタの場合は、本来「有って欲しくない」パラメータなのです。では何故S12が無視できない大きさになってしまうのでしょうか?

多くの教科書にはざっくりと「高周波ではトランジスタの内部容量が帰還容量となるため、増幅器として使用した場合に不安定になる」と書かれています。この「内部容量」というのがS12の主な正体なのですが、「内部容量」とは何者なのでしょうか?

(1) 内部容量とは何か

内部容量とは主にトランジスタのコレクタとベースの間に寄生するキャパシタンスの事です。

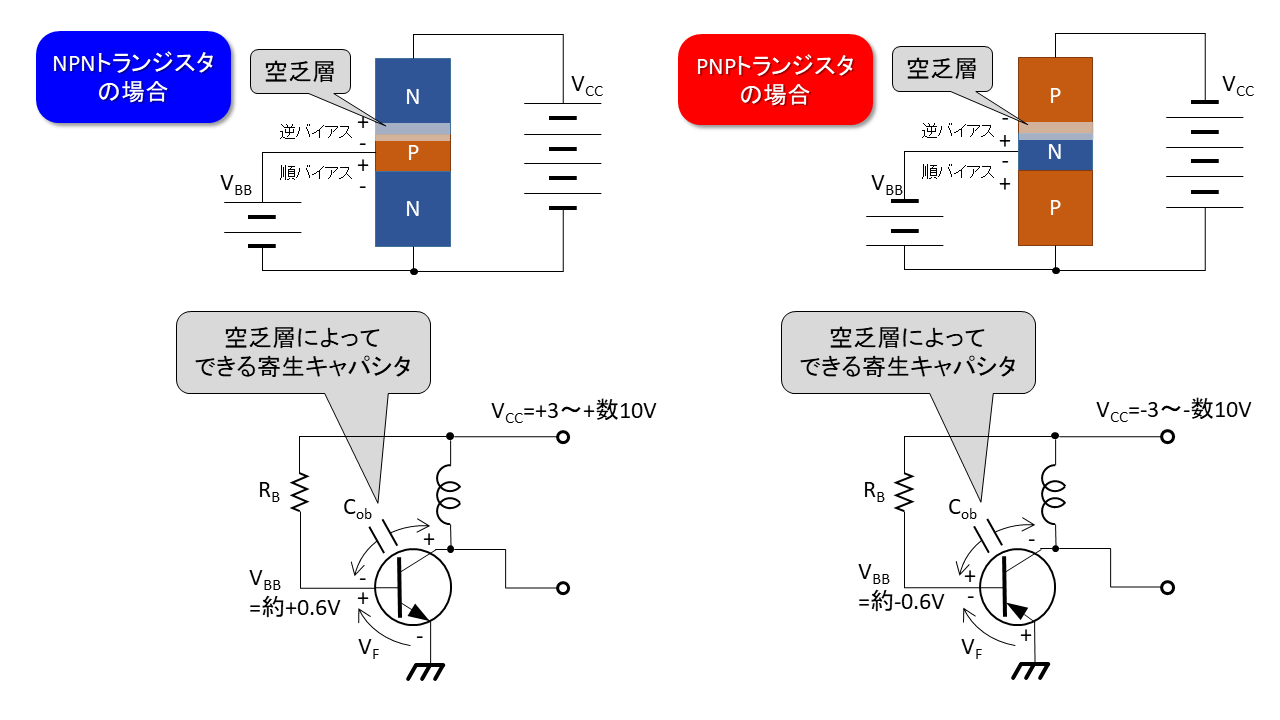

図2はトランジスタをエミッタ共通(エミッタ接地)の増幅器として使用する時の直流バイアス電圧の関係を示します。NPNトランジスタの場合、エミッタを基準にコレクタが最も電圧が高く、ベースはバイアス電流を流す必要があるので、B-E間の接合電圧分だけ高い電圧が印加されます。pn接合と電圧の関係で整理すると、コレクタ-ベース間は逆バイアス、ベース-エミッタ間は順バイアスになっています。

可変容量ダイオード(バリキャップ)の動作原理を思い出してください。pn接合部に逆バイアスがかかっているということは、この接合部分はキャパシタに見えているということになります。

トランジスタが増幅器として能動領域で動作している間は、コレクタ-ベース間のpn接合部は常に逆バイアスとなっている。つまり等価的にコレクタ-ベース間は寄生キャパシタで接続されているのです。これが教科書に書かれている「内部容量」の正体です。このため実際のトランジスタでは、出力振幅の一部がこのキャパシタを介して入力に戻ってしまいます。これがS12の一番目の正体です。

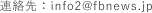

このコレクタ-ベース間に寄生する容量は、トランジスタのデータシートではコレクタ出力容量Cobとして表記されているのが一般的です。図3にアマチュア無線の工作記事などでおなじみの2SC1815(東芝)※1のデータシートを抜粋して示します。

図3 2SC1815のCob(赤く囲った部分)

※1: 東芝製の2SC1815は既に生産終了しており、現在は台湾のUTC社がセカンドソース供給しています。

http://www.utc-ic.com/2011/1013/2SC1815.html

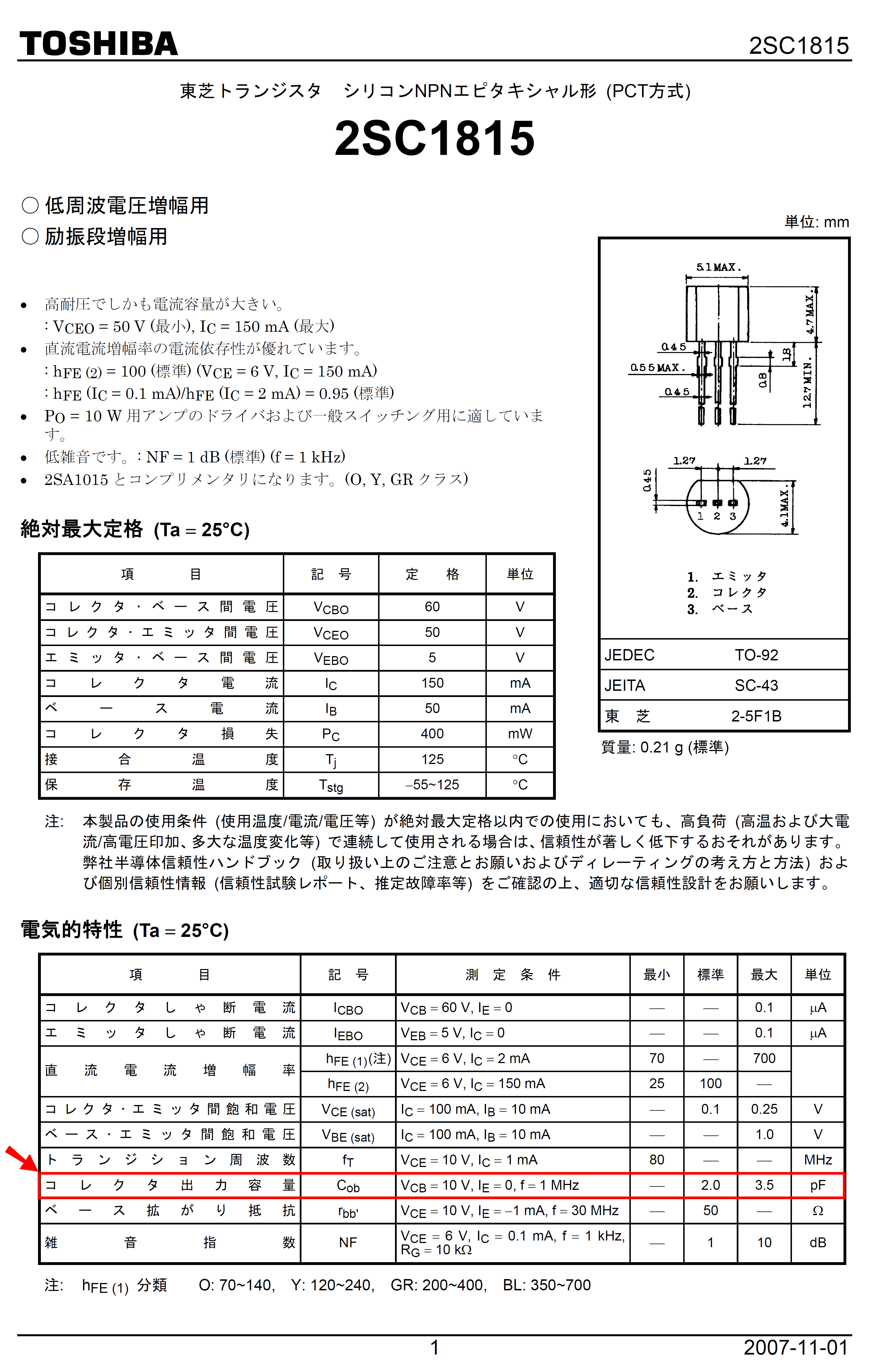

Cobはコレクタ-ベース間の逆バイアスによって生じるため、可変容量ダイオードと同様、コレクタ電圧(VCB)でその大きさが変わり、VCBが小さいほど大きな値になります。今回、本稿で題材とした2SC3356は用途がRF用なので、このあたりは詳しく記載されていてCobではなく、Reverse Transfer Capacitance: Cre(Collector to base capacitance when the emitter grounded)として代表値とグラフが添付されています(図4)。括弧書きの内容から考えてCobよりも用途に即した値であると考えて良いでしょう(一般にCobはエミッタをオープンにして測定します)。グラフからVCBが大きくなるほどキャパシタンスが小さくなる傾向がお判り頂けると思います。また高周波トランジスタなので、図3の2SC1815のCobと比較して小さな値になっています。

図4 2SC3356のCre(データシートから抜粋※2)

※2 データシートのURLは第16話参照

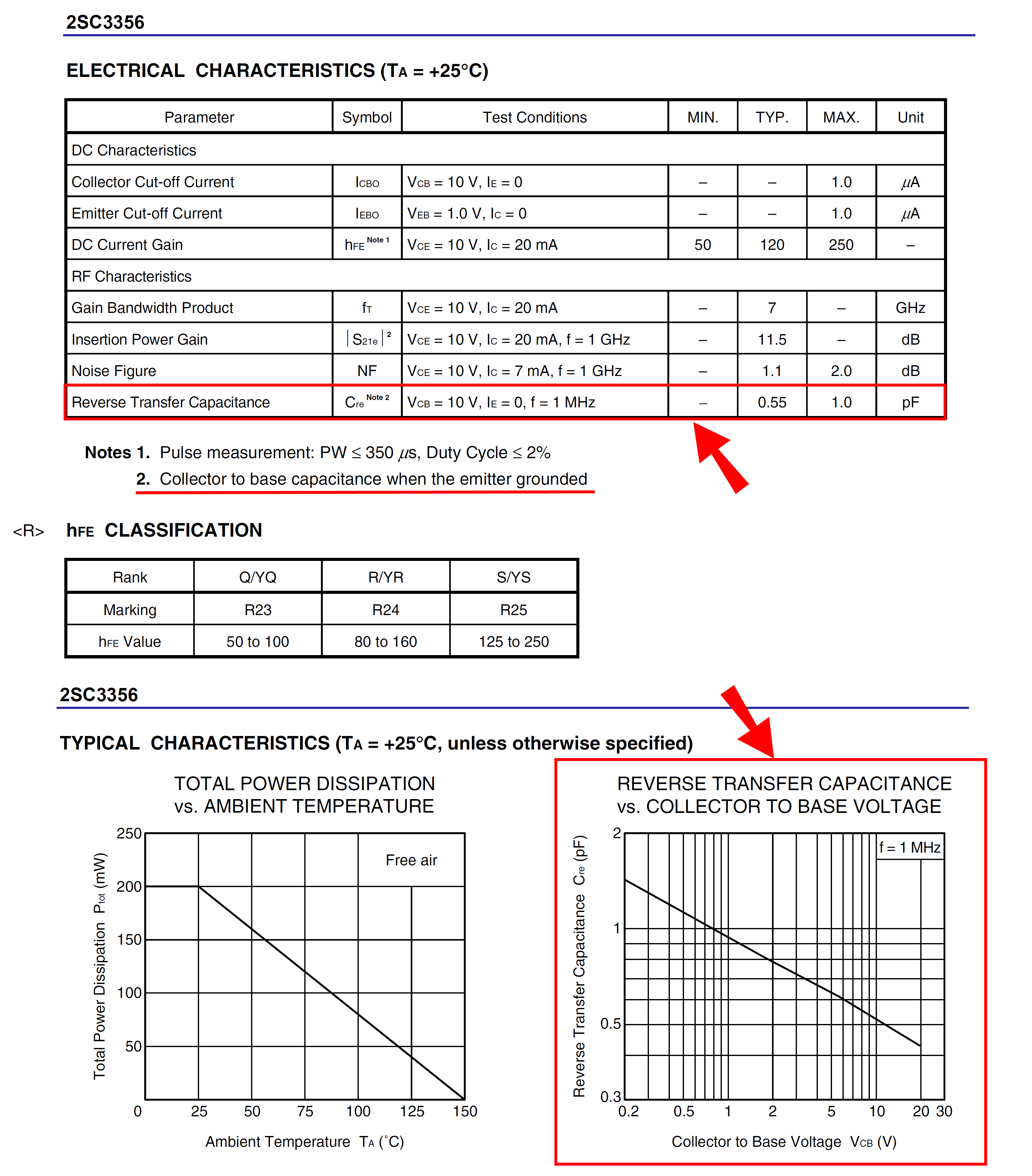

ちなみにFET(電界効果トランジスタ)の場合はどうでしょうか?

図5に示すように、FETの場合も結果は同じです。接合型FET(J-FET)の場合はゲート電極が最も低電位となるので、D-G間、G-S間共に空乏層が生じて寄生キャパシタとなります。またMOS型FETの場合は、そもそもゲート端子が絶縁されていますのでゲートと各端子の間には寄生キャパシタンスが存在します。またチャネルを構成する領域はNPN構造(PチャネルFETの場合はPNP構造)なので、バイポーラトランジスタと同様、ドレイン領域に空乏層が生成されます。

図5 能動領域におけるFETの各端子の電圧の関係

(左: 接合型FET、右: MOS(E-mode)FET)

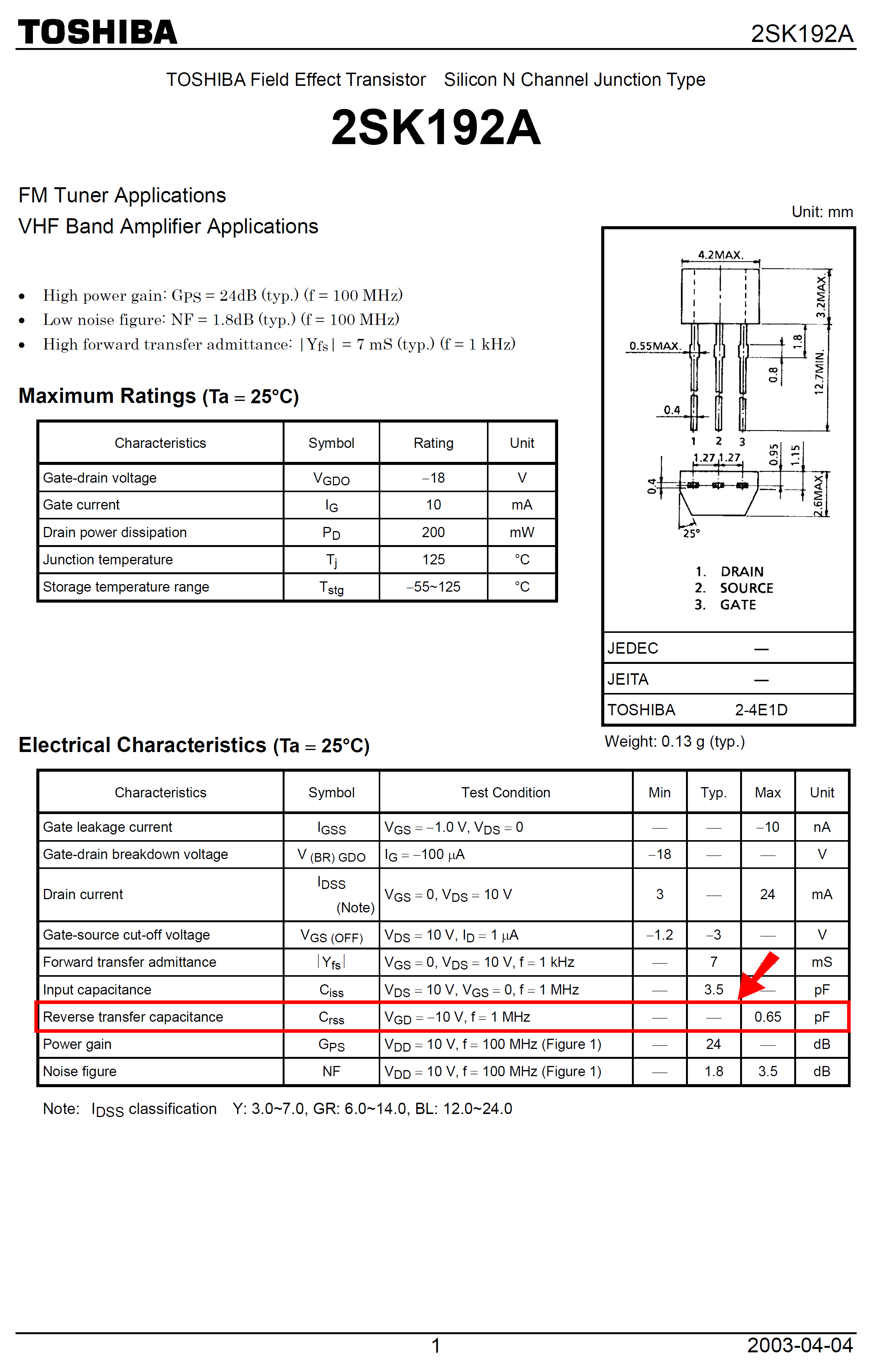

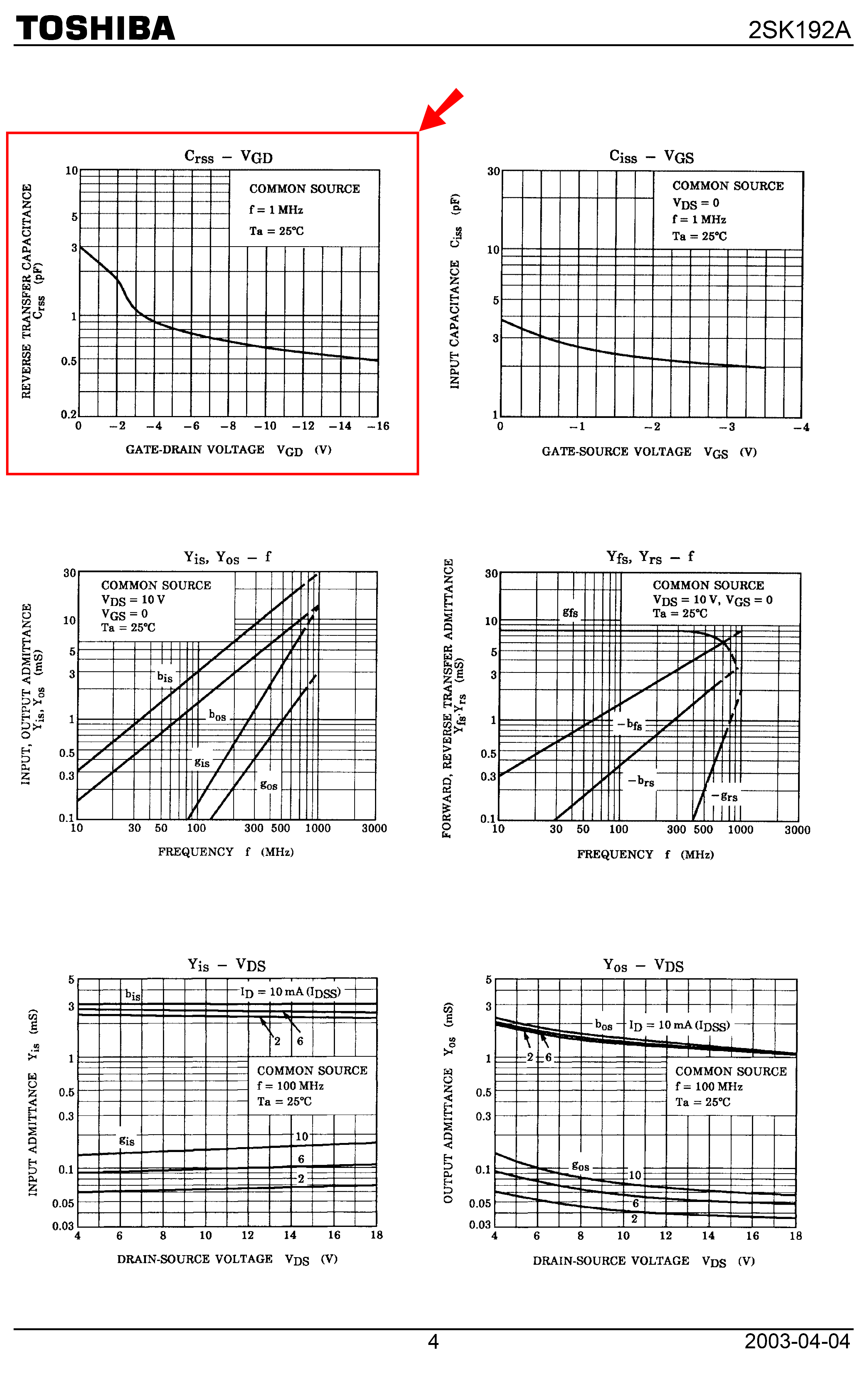

FETの場合はD-G間に寄生するキャパシタを逆伝達キャパシタンス(Crss)、G-S間に寄生するキャパシタンスを入力キャパシタンス(Ciss)と呼びます。FETにおいては、S12の正体はCrssと言うことになります。図6~7にアマチュア無線の工作記事によく登場する2SK192A(東芝製Nch J-FET)※3のデータシートからCrssの規定を抜粋します。2SC3356と同様、高周波用のトランジスタなので、小さな値であることがわかります。

図6 2SK192AのCrss(データシートから抜粋)

図7 2SK192AのCrss(データシートから抜粋)

※3 このデバイスは秋葉原などで若干流通していますが、既に製造中止品です。

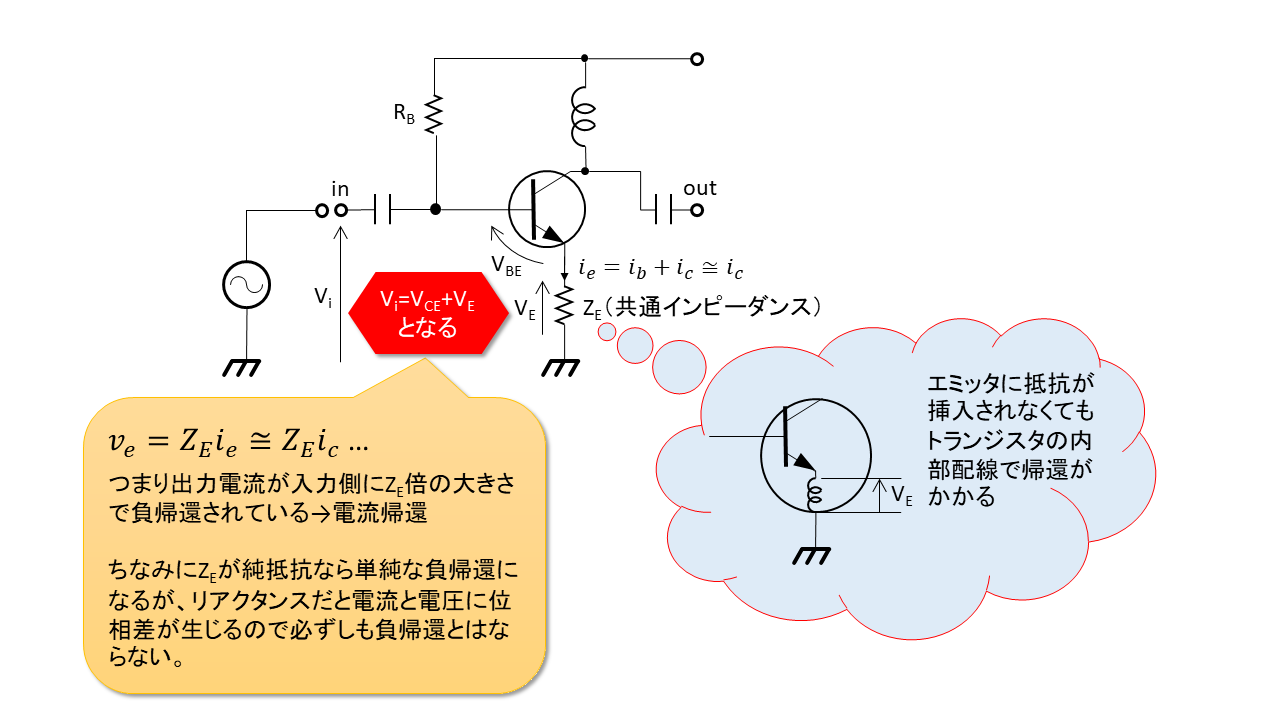

(2) もう一つの正体: 共通インピーダンス

高周波トランジスタのS12が大きな値になる最大の理由はCobの存在です。共通インピーダンスは大半がトランジスタの外の回路で発生するものなので、トランジスタ単体のS12を大きくする直接要因とはいえないですが、トランジスタの内部構造によっては影響しているケースがあります。

エミッタ接地の場合、共通インピーダンスとはエミッタ~GNDまでの配線インピーダンスです。図8に入出力結合のメカニズムを示します。

エミッタの共通インピーダンスは直流的には負帰還になるのでバイアス回路では熱安定特性を確保するために積極的に利用します(電流帰還型バイアス回路)。一方で高周波回路では、トランジスタのリードインダクタンスやエミッタ端子からGNDまでの配線インダクタンスが無視できず、共通インピーダンスが複素数になる結果、必ずしも負帰還とならない場合があります。一般に高周波トランジスタのエミッタ端子や高周波FETのソース端子が底面電極や放熱フランジになっていて、直接GNDにとりつくような構造になっている理由は、この共通インピーダンスを減らす事が目的です。

3. S12をキャンセルする

S12が大きくなる理由が主にCobである事は判りました。ではCobの影響を減らすにはどうすれば良いのでしょうか。Cobの影響を外部回路でキャンセルする方法は大きく2つあり、一つが「中和」、もう一つが「カスケード増幅」です。

(1) 中和回路

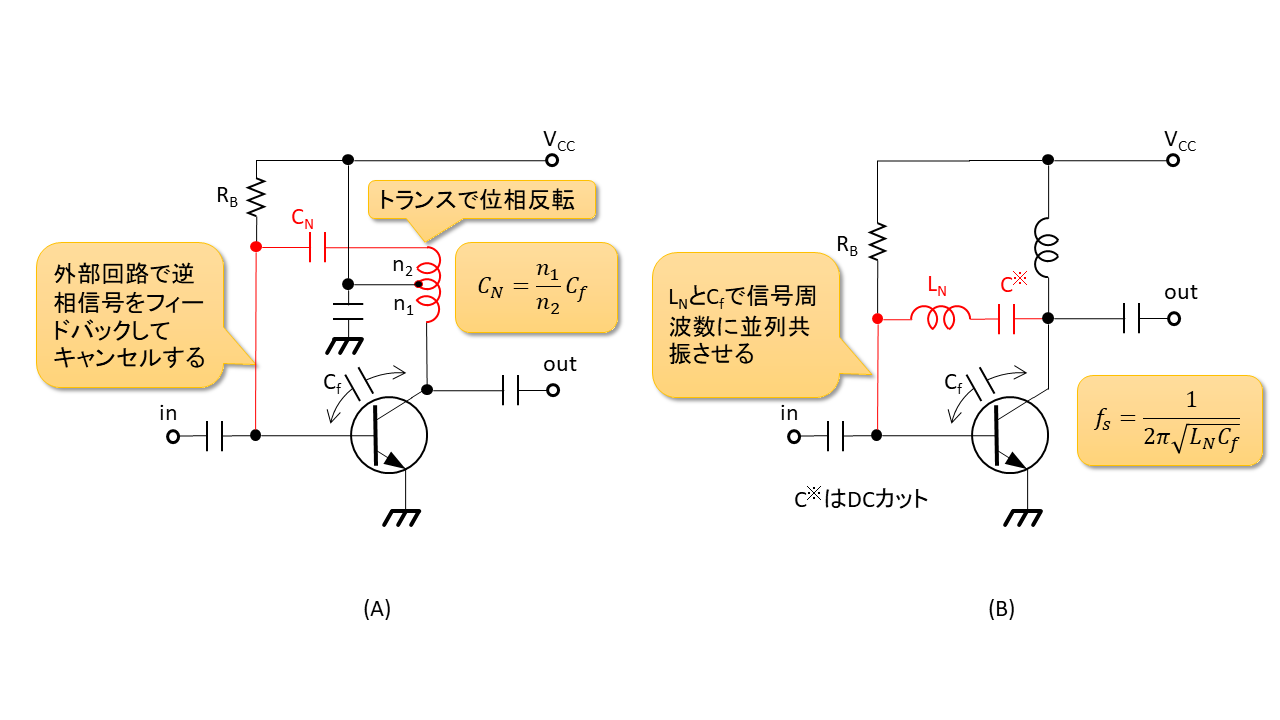

高周波増幅回路では「中和」を行う…とは、アマチュア無線技士の教科書にも登場するくだりですが、何やら混ぜ物をして妖しく処理するようなネーミングですね。代表的な中和回路を図9に示します。FETにおいても同様の回路が使用されます。

※4 回路を見やすくする目的でチョークインダクタ、バイパスコンデンサ、入出力整合回路は省略しています。

図に示した回路構成以外にも色々存在しますが、大きく、以下に示す2つの考え方があります。

① S12を相殺するような(伝達利得の絶対値が等しくて、位相回転が逆相になる)特性のフィードバック回路を追加する。(図9の(A))

② Cobと並列にインダクタをおいて並列共振させる。(図9の(B))

一般的には①の考え方が主流だと思います。出力の一部を入力に注入して相殺(中和)する…というのが「中和回路」の名前の由来です。②の考え方は一見わかりやすいですが、狭帯域になる(そもそも中和回路は狭帯域ですが)ので調整が必要な上、コレクタとベースの間をインダクタで接続するので直流バイアスのデカップリングを考えると意外に設計が面倒になります。 中和によるS12のキャンセルはUHF帯までの狭帯域増幅回路でよく用いられています。

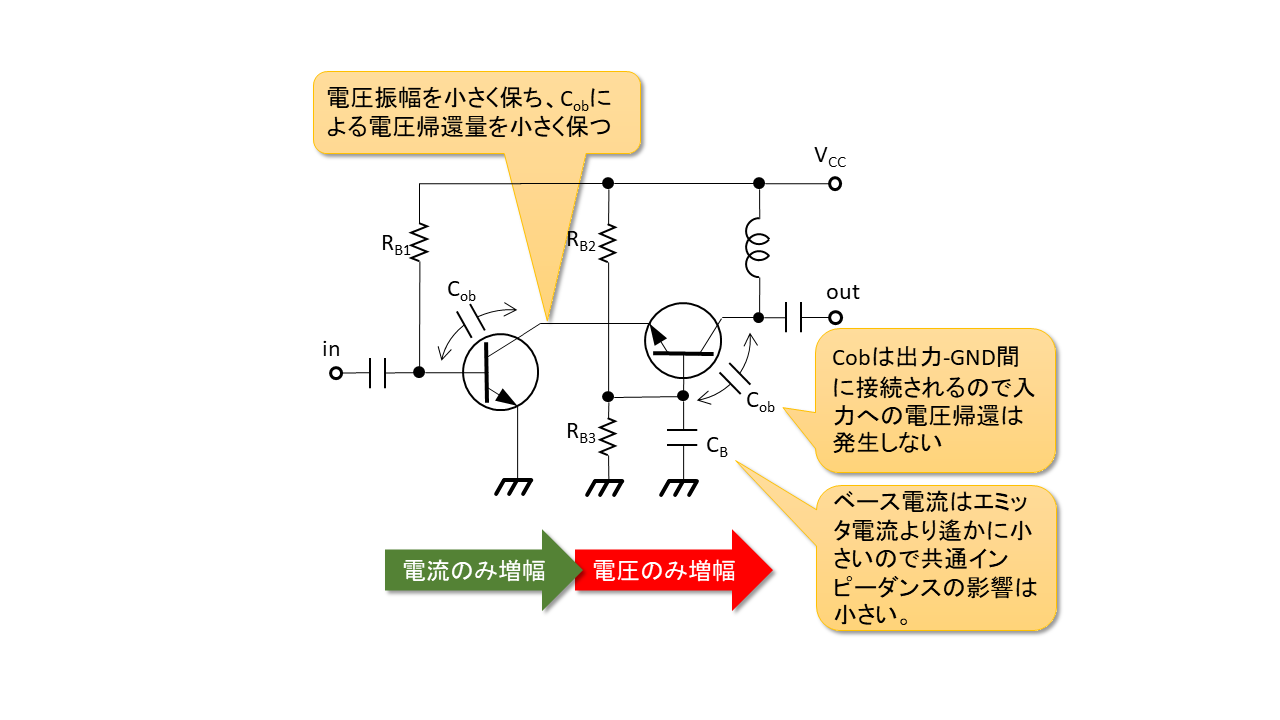

(2) カスケード(Cascade=縦型)増幅

日本語ではカスコード接続とも表記します。広帯域増幅を行う必要があって中和回路の適用が困難な場合は、図10に示すようなカスケード増幅回路を使用する場合がよくあります。これはエミッタ接地の増幅器とベース接地の増幅器を直列(カスケード)接続したもので、ベース接地増幅器の入力インピーダンスが低い特性を利用してS12を小さくしています。電源~GND間にトランジスタを2個直列接続したような回路構成からこの名前で呼ばれます。

※5 回路を見やすくする目的でチョークインダクタ、バイパスコンデンサ、入出力整合回路は省略しています。

すなわち

① 前段のエミッタ接地増幅器のコレクタにはインピーダンスの低いベース接地増幅器のエミッタが接続されるので、大きな電圧振幅が発生しない。

② この結果、前段のコレクタからCobを介してフィードバックされる電圧振幅は非常に小さくなって(正しくは小さくなるところまでコレクタの電圧振幅を小さく設計する)帰還量を下げることができる。

③ 前段のコレクタの電圧振幅は小さいが、後段のベース接地増幅器のコレクタは負荷抵抗を大きくすることができるので、通常のエミッタ接地増幅器と同様の電圧振幅を出力することができる。(エミッタ接地増幅器で電流増幅、ベース接地増幅器で電圧増幅を分担しているイメージ)

④ 後段のベース接地増幅器はベースがGNDに接続されているのでCobで入出力が結合されない。

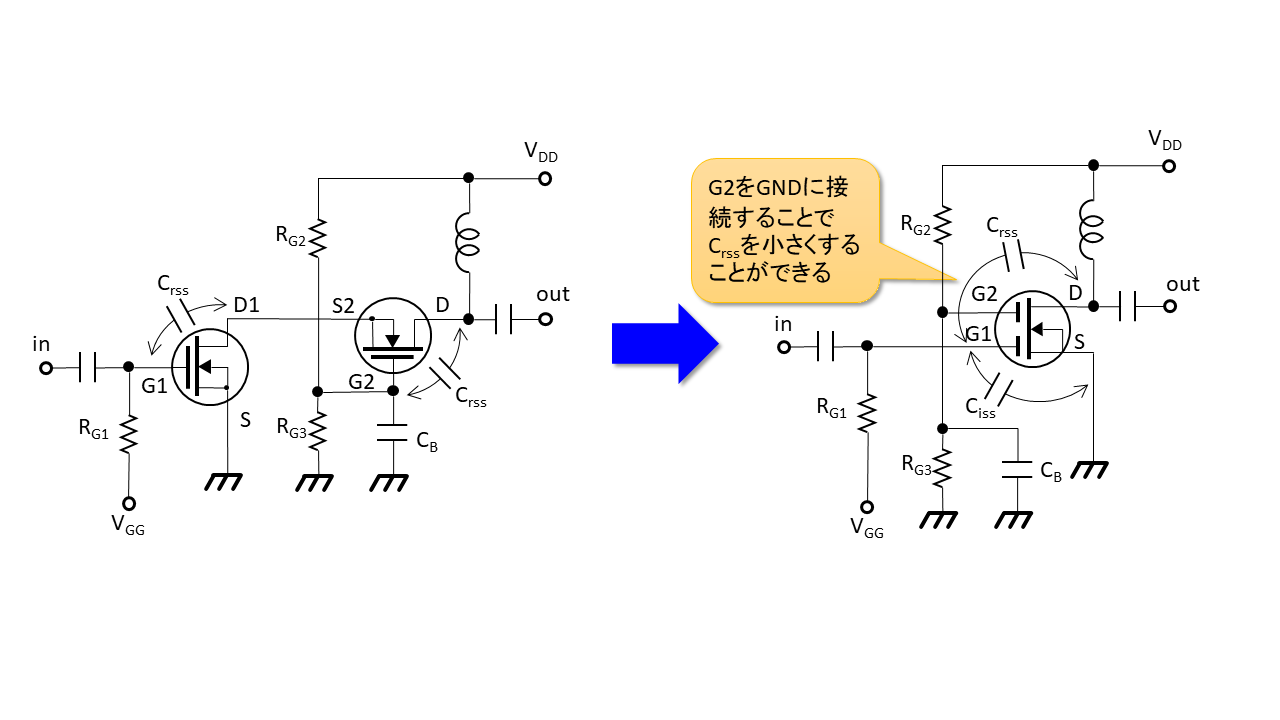

実はVHF帯でよく利用されるデュアルゲートのMOS FETは1個のデバイスの中にカスケード増幅回路を構成したもので、第2ゲートを高周波的に接地することでS12をキャンセルすることが可能です(図11)。なおカスケードアンプの入出力整合をとるためには、カスケード接続した状態でSパ ラメータを取得する必要があります。

図11 MOS FETによるカスケード増幅回路※6

(左)シングルゲートFETによる構成、(右)デュアルゲートFETによる構成

※6 回路を見やすくする目的でチョークインダクタ、バイパスコンデンサ、入出力整合回路は省略しています。

4. 第18話のまとめ

今回は、トランジスタ増幅器の入出力整合回路設計の話を複雑にするS12の正体と、これをキャンセルする手段が中和である事をお話しました。そもそも+の利得があるデバイスは、逆方向利得が存在すると動作が不安定になる(発振リスクが生じる)ので、UHF帯までの増幅回路は基本的に中和を行うことでS12を無視できる状態(昔は1方向化などと呼びました)にすることが設計の第一歩です。1方向化された増幅回路では、入出力の整合はS11, S22(昔はyパラメータが主流だったのでyie, yoe)に対して行えば良い。これが世の中の教科書や、専門書で、トランジスタの入出力整合回路を設計する時は、トランジスタの入出力インピーダンスをS11、S22として設計する…と書かれている事が多い理由です。

要約すると以下の通りです。

(1) トランジスタ増幅回路の入出力が結合する最大の要因は、コレクタ出力容量Cob(FETでは帰還容量Crss)である。

(2) 実際にS12として観測されるフィードバック利得はCobによる電圧帰還にエミッタ共通インピーダンスによる電流帰還が加味される。

(3) CobやCrssの値はコレクタ(ドレイン)電圧で変化する。従ってS12の値もデバイスの動作点で変化する。

(4) 高周波増幅回路を設計する時は中和回路を用いて帰還を打ち消す(S12≒0にする)。

(5) 中和回路が適用できない場合はカスケード回路等で帰還の影響をなくす。

今回はS12と戦ってこれをキャンセルする手法をご説明しました。取り扱う周波数が順マイクロ波やマイクロ波領域に及ぶと、CobやCrssがどれだけ小さくても、そのリアクタンスが小さくなるために帰還量が無視できなくなったり、フィードバック回路で生じる位相回転の影響が無視できなくなったりして、中和をとることが困難になります。またHPAのように大振幅で動作する増幅器ではCobやCrssの値が信号電圧で大きく変化する為、やはり中和回路が効果的に機能しにくくなります。

次回からはS12と付き合って増幅回路を設計する方法について解説します。書き終わって気づきましたが、今月はMr. Smithを全く使用しませんでした。連載のタイトルに反しますが、来月もMr. Smithの登場機会はないかもしれません。あしからずご了承ください。

Mr. Smithとインピーダンスマッチングの話 バックナンバー

- 【第40話】 (連載最終話) インピーダンスマッチングの四方山話

- 【第39話】 アンテナと空間のインピーダンス(その6 平衡と不平衡(その2))

- 【第38話】 アンテナと空間のインピーダンス(その6 平衡と不平衡(その1))

- 【第37話】 アンテナと空間のインピーダンス(その5 放射抵抗と給電抵抗)

- 【第36話】 アンテナと空間のインピーダンス(その4 アンテナの放射抵抗)

- 【第35話】 アンテナと空間のインピーダンス(その3 放射電力と空間のインピーダンス)

- 【第34話】 アンテナと空間のインピーダンス(その2 ダイポールアンテナ)

- 【第33話】 アンテナと空間のインピーダンス(その1 電磁波とは何か)

- 【第32話】 低雑音増幅器(LNA)のインピーダンスマッチング(その7・LNAの設計(後編))

- 【第31話】 低雑音増幅器(LNA)のインピーダンスマッチング(その6・LNAの設計 (前編))

- 【第30話】 低雑音増幅器(LNA)のインピーダンスマッチング(その5・定NF円)

- 【第29話】 低雑音増幅器(LNA)のインピーダンスマッチング(その4・ノイズパラメータ)

- 【第28話】 低雑音増幅器(LNA)のインピーダンスマッチング(その3・NFマッチ)

- 【第27話】 低雑音増幅器(LNA)のインピーダンスマッチング(その2・NFとSN比)

- 【第26話】 低雑音増幅器(LNA)のインピーダンスマッチング(その1・雑音とは何か)

- 【第25話】 そのインピーダンス、本当に存在しますか? (その2)

- 【第24話】 そのインピーダンス、本当に存在しますか? (その1)

- 【第23話】 トランジスタの利得とミスマッチの関係

- 【第22話】 トランジスタの出力インピーダンスと負荷インピーダンス

- 【第21話】 S12と付き合う(その3)

- 【第20話】 S12と付き合う(その2)

- 【第19話】 S12と付き合う(その1)

- 【第18話】 S12の正体

- 【第17話】 増幅器とSパラメータ(その2)

- 【第16話】 増幅器とSパラメータ(その1)

- 【第15話】 Qとは何か(その3)

- 【第14話】 Qとは何か(その2)

- 【第13話】 Qとは何か(その1)

- 【第12話】 λ/4線路の共振と分布定数回路(その2)

- 【第11話】 λ/4線路の共振と分布定数回路(その1)

- 【第10話】 Sパラメータの基礎

- 【第9話】 直列共振と並列共振 その2

- 【第8話】 直列共振と並列共振

- 【第7話】 スミスチャートは日本人の発明?

- 【第6話】 スミスチャートとは何か(その2)

- 【第5話】 伝送線路と反射係数(その2)

- 【第4話】 伝送線路と反射係数

- 【第3話】 スミスチャートとは何か(その1)

- 【第2話】 インピーダンスマッチングの方法

- 【第1話】 なぜインピーダンスマッチング?

お知らせ

-

2022.11.15

11月号後半の記事をアップしました

-

2022.11.1

11月号の記事をアップしました

-

2022.10.17

10月号後半の記事をアップしました

-

2022.10.3

10月号の記事をアップしました

-

2022.9.15

9月号後半の記事をアップしました

-

2022.9.1

9月号の記事をアップしました

-

2022.8.15

8月号後半の記事をアップしました

-

2022.8.1

8月号の記事をアップしました

-

2022.7.15

7月号後半の記事をアップしました

-

2022.7.1

7月号の記事をアップしました

-

2022.6.15

6月号後半の記事をアップしました

トップページに表示する表紙写真を募集中です。横1000x縦540ピクセルのサイズでご自慢の写真をメール添付でご送付ください。(infoアットマークfbnews.jp) 採用者には、月刊FB NEWSロゴ入りマグネットバーを送らせていただきます。 なお「撮影者: JL3ZGL」の様に表記させていただきますが、表記不要の方は、その旨合わせてご連絡ください。 -

2022.6.1

6月号の記事をアップしました

6月4日(土)、JH1CBX/3が14MHz SSBに初オンエアします。 入感がありましたらぜひお声がけください。 -

2022.5.16

5月号後半の記事をアップしました

-

2022.5.2

5月号の記事をアップしました

5月14日(土)、JL3ZGLはオペレーターにMasacoさんを迎えHAMtte交信パーティに 参加します。詳しくは4月号のニュースをご確認ください。 -

2022.4.15

4月号後半の記事をアップしました

-

2022.4.1

4月号の記事をアップしました

-

2022.3.15

3月号後半の記事をアップしました

-

2022.3.1

3月号の記事をアップしました

-

2022.2.15

2月号後半の記事をアップしました

-

2022.2.1

2月号の記事をアップしました

-

2022.1.17

1月号後半の記事をアップしました

-

2022.1.5

1月号の記事をアップしました

トップページに表示する表紙写真を募集中です。横1000x縦540ピクセルのサイズでご自慢の写真をメール添付でご送付ください。(infoアットマークfbnews.jp) 採用者には、月刊FB NEWSロゴ入りマグネットバーを送らせていただきます。 なお「撮影者: JA3YUA」の様に表記させていただきますが、表記不要の方は、その旨合わせてご連絡ください。 -

2021.12.15

12月号後半の記事をアップしました

-

2021.12.1

12月号の記事をアップしました

-

2021.11.15

11月号後半の記事をアップしました

-

2021.11.01

2021年11月号の記事をアップしました

-

2021.10.15

10月号後半の記事をアップしました

-

2021.10.01

2021年10月号の記事をアップしました

-

2021.09.15

9月号後半の記事をアップしました

-

2021.09.01

2021年9月号の記事をアップしました

-

2021.08.16

8月号後半の記事をアップしました

-

2021.08.02

2021年8月号の記事をアップしました

-

2021.07.15

7月号後半の記事をアップしました

-

2021.07.01

2021年7月号の記事をアップしました

-

2021.06.15

6月号後半の記事をアップしました

-

2021.06.01

2021年6月号の記事をアップしました

-

2021.05.17

5月号後半の記事をアップしました

-

2021.05.06

2021年5月号の記事をアップしました

-

2021.04.15

4月号後半の記事をアップしました

-

2021.04.01

2021年4月号の記事をアップしました

連載記事 Masacoの「むせんのせかい」はコロナ禍の影響により、取材ができない状況が続いており、状況が改善されるまで不定期掲載とさせていただきます。よろしくお願いいたします。 -

2021.03.15

3月号後半の記事をアップしました

連載記事「今月のハム」はコロナ禍の影響により、取材ができない状況が続いており、状況が改善されるまで不定期掲載とさせていただきます。よろしくお願いいたします。 -

2021.03.01

2021年3月号の記事をアップしました

-

2021.02.15

2月号後半の記事をアップしました

-

2021.02.01

2021年2月号の記事をアップしました

-

2021.01.15

1月号後半の記事をアップしました

-

2021.01.05

2021年1月号の記事をアップしました

-

2020.12.15

12月号後半の記事をアップしました

-

2020.12.01

2020年12月号の記事をアップしました

-

2020.11.16

11月号後半の記事をアップしました

-

2020.11.02

2020年11月号の記事をアップしました

-

2020.10.15

10月号後半の記事をアップしました

-

2020.10.01

2020年10月号の記事をアップしました

-

2020.09.15

9月号後半の記事をアップしました

-

2020.09.01

2020年9月号の記事をアップしました

-

2020.08.17

8月号後半の記事をアップしました

-

2020.08.03

2020年8月号の記事をアップしました

-

2020.07.15

7月号後半の記事をアップしました

-

2020.07.01

2020年7月号の記事をアップしました

-

2020.06.15

6月号後半の記事をアップしました

-

2020.06.01

2020年6月号の記事をアップしました

-

2020.05.01

2020年5月号の記事をアップしました

-

2020.04.15

4月号後半の記事をアップしました

-

2020.04.01

2020年4月号の記事をアップしました

-

2020.03.16

3月号後半の記事をアップしました

-

2020.03.09

JARD、eラーニングでのアマチュア無線国家資格取得を呼び掛けるお知らせを、臨時休校で自宅待機中の小中高生に向けて発表。詳しくはこちら。

-

2020.03.02

2020年3月号の記事をアップしました

-

2020.02.17

2月号後半の記事をアップしました

-

2020.02.03

2020年2月号の記事をアップしました

-

2020.01.15

1月号後半の記事をアップしました

-

2020.01.06

2020年1月号の記事をアップしました

-

2019.12.16

12月号後半の記事をアップしました

-

2019.12.02

2019年12月号の記事をアップしました

-

2019.11.15

11月号後半の記事をアップしました

-

2019.11.01

2019年11月号の記事をアップしました

-

2019.10.15

10月号後半の記事をアップしました

-

2019.10.01

2019年10月号の記事をアップしました

-

2019.09.17

9月号後半の記事をアップしました

-

2019.09.02

2019年9月号の記事をアップしました

-

2019.08.16

8月号後半の記事をアップしました

-

2019.08.01

2019年8月号の記事をアップしました

-

2019.07.16

7月号後半の記事をアップしました

-

2019.07.01

2019年7月号の記事をアップしました

-

2019.06.17

6月号後半の記事をアップしました

-

2019.06.01

2019年6月号の記事をアップしました

-

2019.05.20

5月号後半の記事をアップしました

-

2019.05.07

2019年5月号の記事をアップしました

-

2019.04.15

4月号後半の記事をアップしました

-

2019.04.01

2019年4月号の記事をアップしました

-

2019.03.15

3月号後半の記事をアップしました

-

2019.03.01

2019年3月号の記事をアップしました

-

2019.02.15

2月号後半の記事をアップしました

-

2019.02.01

2019年2月号の記事をアップしました

-

2019.01.18

1月号後半の記事をアップしました

-

2019.01.07

2019年1月号の記事をアップしました

-

2018.12.17

12月号後半の記事をアップしました

-

2018.12.01

2018年12月号の記事をアップしました

-

2018.11.15

11月号後半の記事をアップしました

-

2018.11.01

2018年11月号の記事をアップしました

-

2018.10.15

10月号後半の記事をアップしました

-

2018.10.01

2018年10月号の記事をアップしました

-

2018.09.15

9月号後半の記事をアップしました

-

2018.09.01

2018年9月号の記事をアップしました

-

2018.08.17

8月号後半の記事をアップしました

-

2018.08.01

2018年8月号の記事をアップしました

-

2018.07.17

7月号後半の記事をアップしました

-

2018.07.02

2018年7月号の記事をアップしました

-

2018.06.15

6月号後半の記事をアップしました

-

2018.06.01

2018年6月号の記事をアップしました

-

2018.05.15

5月号後半の記事をアップしました

-

2018.05.01

2018年5月号の記事をアップしました

-

2018.04.16

4月号後半の記事をアップしました

-

2018.04.02

2018年4月号の記事をアップしました

-

2018.03.15

3月号後半の記事をアップしました

-

2018.03.01

2018年3月号の記事をアップしました

-

2018.02.15

2月号後半の記事をアップしました

-

2018.02.01

2018年2月号の記事をアップしました

-

2018.01.15

1月号後半の記事をアップしました

-

2018.01.05

2018年1月号の記事をアップしました

-

2017.12.15

12月号後半の記事をアップしました

-

2017.12.1

12月号をアップしました

-

2017.11.15

11月号後半の記事をアップしました

-

2017.11.1

11月号をアップしました

-

2017.10.16

10月号後半の記事をアップしました

-

2017.10.2

10月号をアップしました

-

2017.9.15

What a healthy time! ~健康を応援する特別なお料理~/第3回 食物繊維たっぷり! 海藻の和風リゾット、FB Monthly Fashion/第9回 秋っぽい柄&色コーデ、子供の無線教室/第9回 「アンテナの形や大きさに注目!!」を掲載しました

-

2017.9.4

<速報>ハムフェア2017を掲載しました

-

2017.9.1

9月号をアップしました

-

2017.8.17

What a healthy time! ~健康を応援する特別なお料理~/第2回 和風のポトフ 納豆ソース添え、FB Monthly Fashion/第8回 夏のお出かけコーデ、子供の無線教室/第8回 「無線機にはどんなものがあるの?」を掲載しました

-

2017.8.1

8月号をアップしました

-

2017.7.18

What a healthy time! ~健康を応援する特別なお料理~/第1回 メロンの冷製スープ ナッツのアイスクリームのせ、FB Monthly Fashion/第7回 コットンTシャツコーデとボーイズコーデ、子供の無線教室/第7回 「電波はどうやって海外や宇宙に届くの?」を掲載しました

-

2017.7.1

7月号をアップしました

-

2017.6.15

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第9回 FB Girlsの野望 with ムースと甘エビのタルタル、FB Monthly Fashion/第6回 雨の日コーデと親子コーデ、子供の無線教室/第6回 「電波はいろいろなところで大活躍!!」を掲載しました

-

2017.6.1

6月号をアップしました

-

2017.5.15

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第8回 番外編 春うらら♪豪華弁当でお花見、FB Monthly Fashion/第5回 ブラウス&シャツを使ったコーディネート、子供の無線教室/第5回 「周波数によって変わる、電波の特徴」を掲載しました

-

2017.5.1

5月号をアップしました

-

2017.4.17

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第7回 ARDFの思い出 with 2種類のソースのカルボナーラ、FB Monthly Fashion/第4回 Gジャンを使ったコーディネート、子供の無線教室/第4回 「電波の性質を覚えよう」を掲載しました

-

2017.4.1

4月号をアップしました

-

2017.3.15

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第6回 初めてのQSOの思い出 with グリーンのアクアパッツァ、FB Monthly Fashion/第3回 ピンクを使ったコーディネート、子供の無線教室/第3回 「電波はどうやって伝わるの?」を掲載しました

-

2017.3.1

3月号をアップしました

-

2017.2.15

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第5回 FB Girlsの試験の思い出 withウマ辛和風スープ、FB Monthly Fashion/第2回 デニムと明るめニットのコーディネートを掲載しました

-

2017.2.1

2月号をアップしました

-

2017.1.16

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第4回 YLハムを増やす秘策とは?! withおなかにやさしいお料理、【新連載】FB Monthly Fashion/第1回 アウター別おすすめコーディネート(ライダース・ノーカラー・ダッフル)を掲載しました

-

2017.1.5

1月号をアップしました

-

2016.12.15

What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第3回 YLハムの行く年来る年 with ブイヤベースの洋風お鍋を掲載しました

-

2016.12.1

12月号をアップしました

-

2016.11.15

FB Girlsが行く!!~元気娘がアマチュア無線を体験~/<第3話>元気娘、秋の休日を楽しむ!!(後編)!、What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第2回 YLハムの悩み解決!with サケのフレンチトーストを掲載しました

-

2016.11.1

11月号をアップしました

-

2016.10.17

FB Girlsが行く!!~元気娘がアマチュア無線を体験~/<第3話>元気娘、秋の休日を楽しむ!!(前編)!、【新連載】What a tasty time! ~グルメYLたちのGirl'sトーク♥~/第1回 FB GirlsのプライベートQSO with 土瓶蒸しのリゾットを掲載しました

外部リンク

アマチュア無線関連機関/団体

各総合通信局/総合通信事務所

アマチュア無線機器メーカー(JAIA会員)

次号は 12月 1日(木) に公開予定