今更聞けない無線と回路設計の話

【テーマ1】三角関数のかけ算と無線工学

第15話

位相検波器の話

2023年5月1日掲載

第14話ではPLLの基本動作を解説し、無線通信機での代表的な用途としてジッタフィルタ(位相雑音抑制フィルタ)と周波数シンセサイザについてご紹介しました。このうち周波数シンセサイザにおいては、まとめの項で述べた通り、位相検波器の前段に分周回路が挿入されるため、位相比較器に入力される信号はサイン波ではなく矩形波になります。またVCOの発振周波数範囲が広いため、位相検波の範囲も±90°の範囲ではあっという間に位相検波可能な範囲を逸脱してしまい、初期引き込みに失敗する可能性があります。従って一般的なPLLシンセサイザにおいてはフリップフロップを用いた「位相・周波数検波回路(PFD)」なるものが適用されます。第15話はこのあたりを解説します。

1. 周波数シンセサイザの位相検波器に求められる要件

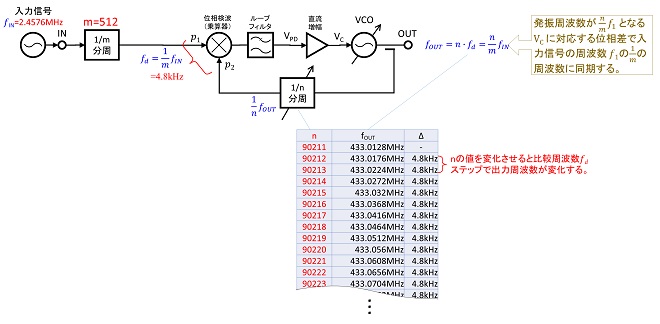

図1は第14話の図4の再掲です。周波数シンセサイザに適用するPLLは位相比較周波数と異なる周波数を出力するため、広い周波数範囲に渡ってループ安定性能(フィードバックループが正しく収束し、発振することなくロック(同期)状態が安定していること)が要求されます。

図1 周波数シンセサイザ

(第14話の図4を再掲)

2. アナログ乗算による位相比較器の問題点

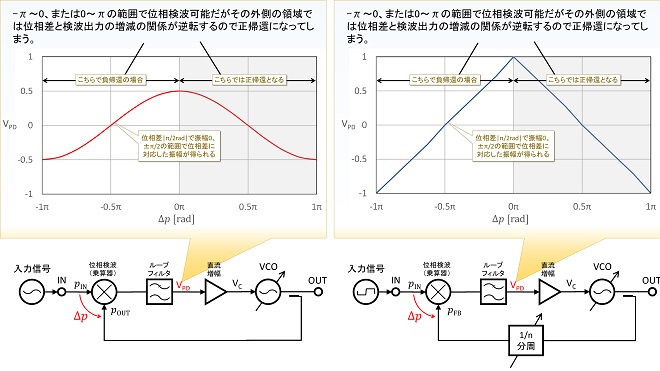

広い周波数帯域に渡ってループ安定を確保する上で重要になってくるのが、位相比較器の検波範囲です。アナログ乗算器の位相検波範囲は図2の右側に示すように+0.5π [rad]または−0.5π [rad]を中心に±0.5π [rad]つまり±90°の範囲でした。アナログ乗算器を位相検波器として適用したPLLにおいては、入力信号P1とフィードバック信号P2の位相差Δ𝑝がこの範囲を超えると位相差Δ𝑝と検波電圧VPDの増減の関係が逆転してしまい、それまで負帰還だったループが正帰還となって発散してしまいます。このため、VCXOを使用した位相雑音フィルタのようにP1の信号とP2の信号の初期周波数差が殆どなければ問題ないのですが、周波数シンセサイザのように起動時の初期周波数に大きな差がある場合、Δ𝑝が急速に大きくなっていくため、ループが同期しにくく(発散しやすく)なってしまいます。

π

図2 アナログ乗算器による位相検波範囲(左: サイン波入力、右: 矩形波入力)

もう一つの問題点が波形の問題です。周波数シンセサイザにおいては位相検波器の前段にデジタル分周器が接続されるため、位相比較の対象はサイン波ではなく矩形波(回路方式によってはパルス波)になります。アナログ乗算器で矩形波同士をかけ算すると、図2の右側に示すように、その結果は位相差Δ𝑝のコサインではなく、位相差がπ [rad]毎に傾きが極性反転する一次関数になります※1。従って矩形波であっても位相検波は可能ですが、これは乗算する波形のデューティ比DFが50%(0.5)であることが前提です。1/nデジタル分周器の出力波形はnが偶数の時にはデューティ比DF=0.5を実現可能ですが、nが奇数の時にはDF≠0.5となってしまい検波電圧に誤差を生じます。まとめると、周波数シンセサイザ用PLLの位相検波器には、アナログ乗算器では実現できない下記の性能が求められます。

- ① 位相差が±2πの範囲は位相差が出力され、それ以上の位相差(つまり周回遅れ(進み)なので周波数が合致していない状態)のときは周波数差が出力される。

- ② 矩形波の位相比較が可能で、検波結果が波形のデューティ比の影響をうけない。

市販のPLL-ICでは、このような特性を実現する為、RSフリップフロップとチャージポンプを用いたPFD(Phase-Frequency Detector : 位相-周波数比較回路)の採用が主流となっています。

3. フリップフロップによる位相比較

フリップフロップ(Flip Flop)とは「パタパタ」とか「カタカタ」に相当する擬音語であり、直訳すると「パタパタ回路」、つまり入力トリガに応じて2つの出力が交互に1/0 0/1と反転し合う回路の総称です。日本語では「順序回路」と翻訳されています。フリップフロップという呼び方は論理回路素子としての呼称で、電子回路としての呼称はマルチバイブレータ・・・ すなわち振動回路という取り扱いになっています。

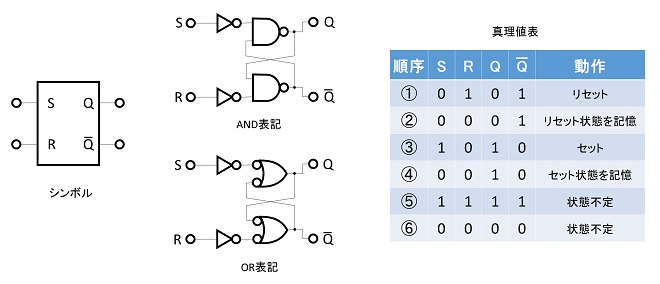

(1) RSフリップフロップ

RSフリップフロップ(RS FF)とはReset/Set Flip-Flopの略称で、入力トリガとしてS(Set)/R(Reset)の2つの端子を持ったフリップフロップです。電子回路の呼称では双安定マルチバイブレータと呼ばれます。図3に論理回路シンボルと等価論理回路、ならびに真理値表を示します。

S端子が0→1に変化するとQ端子が1、

端子が0に変化し、その後S端子が1→0に戻っても、R端子が0→1になるまで出力端子は𝑄端子が1、端子が0の状態を維持します。

R端子が0→1に変化すると𝑄端子が0、端子が1に変化し、その後R端子が1→0に戻っても、S端子が0→1になるまで出力端子は𝑄端子が0、端子が1の状態を維持します。

なお、このフリップフロップはS端子とR端子を同時に1にすると状態不定になります。

図3 RSフリップフロップ

すなわち、S、Rのどちらが最後に1になったかを記憶する回路として動作します。状態が記憶されると言うことは、入力信号の0→1または1→0の変化(波形のエッジ)で動作する回路と見なす事ができます。RSフリップフロップのこの特性を利用することで、入力信号のデューティ比に影響されない位相検波回路を実現することができます。

(2) RSフリップフロップを用いたPFD

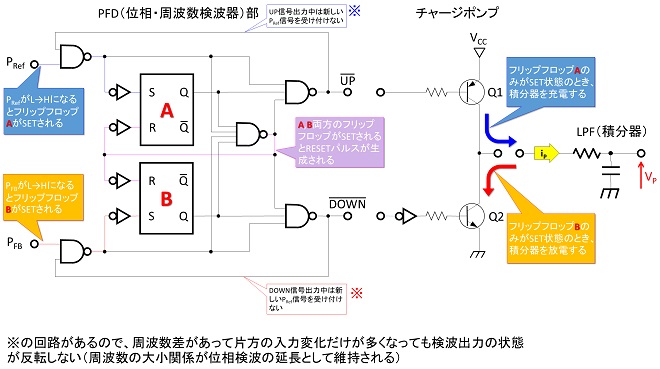

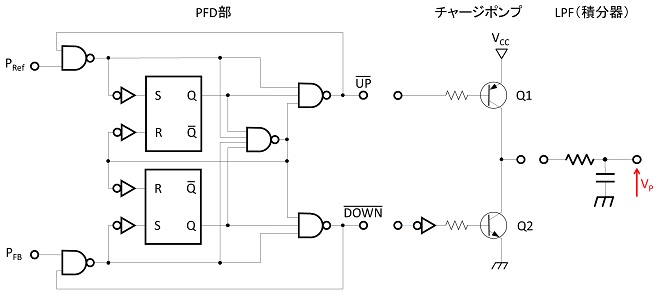

図4にRSフリップフロップを用いた位相検波回路例を示します。この回路はPLLのループフィルタとして機能する積分回路まで含めて位相検波器を実現しており、大きくPFD部、チャージポンプ、LPFの3つのブロックから構成されています。

図4 RSフリップフロップによるPFD

PFDは2つのRSフリップフロップから構成されたロジック回路で、PREF、PFBの2つの入力端子と、の2つの出力端子を有し、PREFに入力される信号の位相を基準にPFBに入力される信号の位相が進んでいる時は端子にLowレベルのパルス、逆の場合は端子にLowレベルのパルスを出力します。チャージポンプ回路は電源に接続されたトランジスタスイッチQ1とGNDに接続されたトランジスタスイッチQ2から構成され※2、PFD部の、パルスに応じて後段のLPFを充放電します。LPFはチャージポンプで充放電されることによって、位相検波電圧を生成すると共に、PLLのループフィルタとしてPLLの応答特性を決定する役割を担います。

(3) PFDの動作

図5にPFDの動作説明を示します。PFD部を構成するA,B 2つのRSフリップフロップは、それぞれPREF信号、PFB信号が0→1に変化したタイミングでセット状態になり、両方のフリップフロップがセット状態になった瞬間にリセットされます。フリップフロップAがセット状態の期間はパルスが、フリップフロップBがセット状態の期間はパルスがチャージポンプに出力されます。

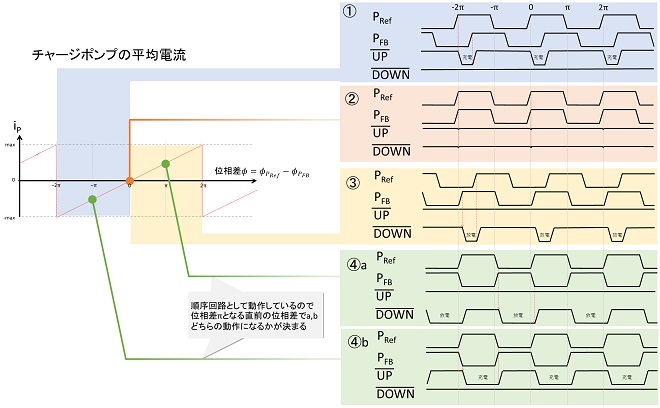

PREF、PFDの位相関係と、パルスの出方、ならびに積分器に出力される充放電電流iPの関係を図6に示します。A,B二つのRSフリップフロップは、入力信号の立ち上がりエッジでのみ状態が変化するため、連続的に位相差を検出できる範囲はアナログ乗算器の±π [rad]から±2π [rad]に拡張されます。立ち上がりエッジにしか応答しないので、検波結果は入力信号波形のデューティ比には影響されません。積分器への充放電電流はPREF入力信号とPFB入力信号の立ち上がりエッジのタイミングが揃ったときに最小かつ同量となります。

PREF入力信号とPFB入力信号の間に周波数差があった場合はどうなるでしょうか。この場合、周波数の高い方の信号が入力されている側のフリップフロップがセットされてから、リセットされるまでの間に複数回セット信号が入力される事になります。RSフリップフロップは一度セット状態に遷移すると、リセットパルスが入るまで、繰り返しセットパルスが入力されても出力の状態は変化しません。つまり高い周波数の信号が入力された側のフリップフロップのセット状態が継続する事になるので、PREFとPFBのどちらの端子に入力されている信号の周波数が高いかが検波されている事になります。

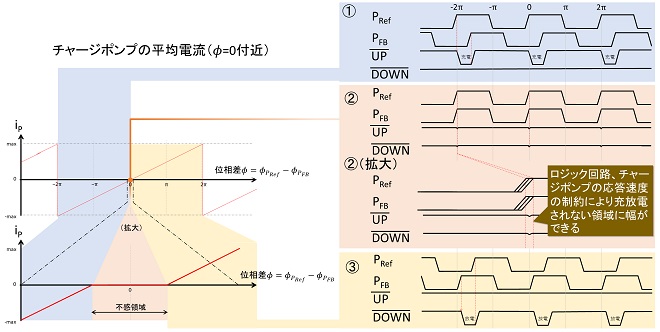

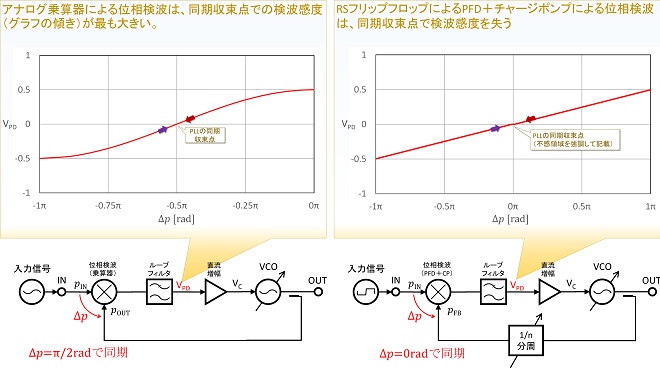

4. 位相検波器の使い分け

RSフリップフロップを用いたPFDは位相検波範囲が±2π [rad]に拡張された上、入力信号に周波数差があって、位相差が±2π [rad]を超えた場合は周波数検波器として位相進み→周波数大、位相遅れ→周波数小の関係に自動的に移行して出力状態を維持してくれるので、動作周波数範囲の広い周波数シンセサイザ用のPLLには理想的な位相検波回路といえます。しかしRSフリップフロップを用いた位相検波器には一つ大きな欠点があります。図7に示すようにPFDは、チャージポンプによる充放電で位相差電圧を作り出しているため、位相差0°付近においては充放電が行われなくなり、微少な位相差に反応しなくなる事です。

この領域はPLLが同期状態のときに、「歯車のバックラッシュ」のような状態を作りだしてしまいます。このため位相雑音(ジッタ)フィルタのような用途のPLLにデジタルPFDを適用すると、出力信号の位相が数度の幅を持ってふらふらするような事象を引き起こしてしまう場合があります(図8)。このような状態を嫌う用途では、不感領域が存在しないアナログ乗算器や排他的論理和演算による位相検波が好まれます。

5. 第15話のまとめ

第15話では、周波数シンセサイザ用PLLのキーデバイスともいえる、デジタル方式の位相検波回路(位相・周波数検波回路)について解説しました。PLLの位相検波回路には、大きく

①アナログ乗算器

②Exclusive OR(EX-OR: 排他的論理和) → ①の動作をデジタル回路で模擬した方式

③JKフリップフロップ → 初期のPFD方式 本稿では説明を割愛

④RSフリップフロップ2個によるPFD

の4方式がありますが、概ね①(または②)と④の間で用途に応じて使い分けされています。

周波数シンセサイザは取り扱う周波数範囲が広く、最初は大きく周波数が異なる状態から位相同期状態に引き込む事が常に要求されます。このような用途において、RSフリップフロップによるPFDは理想的な位相検波方式といえます。

一方で、RSフリップフロップを用いたPFDは同相入力付近に不感領域ができやすく、PLLを構成したときに同期状態においてループゲインが低下する欠点があり、位相雑音(ジッタ)フィルタ用のPLLには不向きだといえます。

次回はループフィルタとPLLの応答特性について解説します。

※1: アナログ乗算器をEX-OR(排他的論理和)ゲートに置き換えても同じ結果になります。

※2: 現在市販のPLL-ICでは、位相検波特性を位相差(波形の時間差)に正確に比例させる為、充電側、放電側共に定電流回路(第10話参照)とするのが主流です。

今更聞けない無線と回路設計の話 バックナンバー

- 【テーマ2】デシベルと無線工学 (第19話) レベルダイヤグラムの縦軸(その3)

- 【テーマ2】デシベルと無線工学 (第18話) レベルダイヤグラムの縦軸(その2)

- 【テーマ2】デシベルと無線工学 (第17話) レベルダイヤグラムの縦軸(その1)

- 【テーマ2】デシベルと無線工学 (第16話) レベルダイヤグラムの構成

- 【テーマ2】デシベルと無線工学 (第15話) 非線形歪み(その5)

- 【テーマ2】デシベルと無線工学 (第14話) 非線形歪み(その4)

- 【テーマ2】デシベルと無線工学 (第13話) 非線形歪み(その3)

- 【テーマ2】デシベルと無線工学 (第12話) 非線形歪み(その2)

- 【テーマ2】デシベルと無線工学 (第11話) 非線形歪み(その1)

- 【テーマ2】デシベルと無線工学 (第10話) 線形歪み(フェージング現象)

- 【テーマ2】デシベルと無線工学 (第9話) 足される雑音と掛けられる雑音

- 【テーマ2】デシベルと無線工学 (第8話) 等価雑音の内訳

- 【テーマ2】デシベルと無線工学 (第7話) 無線通信の成立条件(その3)

- 【テーマ2】デシベルと無線工学 (第6話) 無線通信の成立条件(その2)

- 【テーマ2】デシベルと無線工学 (第5話) 無線通信の成立条件

- 【テーマ2】デシベルと無線工学 (第4話) dBmとdBµVの複雑な関係

- 【テーマ2】デシベルと無線工学 (第3話) dB(デシベル)を知る(その2)

- 【テーマ2】デシベルと無線工学 (第2話) dB(デシベル)を知る(その1)

- 【テーマ2】デシベルと無線工学 (第1話) (プロローグ)無線通信機の天井と床

- 【テーマ1】三角関数のかけ算と無線工学 (第30話) 三角関数のかけ算と無線工学の切っても切れない深い縁

- 【テーマ1】三角関数のかけ算と無線工学 (第29話) 交流ベクトル空間と直交ミキサ(その4)

- 【テーマ1】三角関数のかけ算と無線工学 (第28話) 交流ベクトル空間と直交ミキサ(その3)

- 【テーマ1】三角関数のかけ算と無線工学 (第27話) 交流ベクトル空間と直交ミキサ(その2)

- 【テーマ1】三角関数のかけ算と無線工学 (第26話) 交流ベクトル空間と直交ミキサ

- 【テーマ1】三角関数のかけ算と無線工学 (第25話) マイナスの周波数

- 【テーマ1】三角関数のかけ算と無線工学 (第24話) 同一周波数のサイン波の掛け算と周波数の話(その3)

- 【テーマ1】三角関数のかけ算と無線工学 (第23話) 同一周波数のサイン波の掛け算と周波数の話(その2)

- 【テーマ1】三角関数のかけ算と無線工学 (第22話) 同一周波数のサイン波の掛け算と周波数の話(その1)

- 【テーマ1】三角関数のかけ算と無線工学 (第21話) ループフィルタとPLLの応答特性の話(その6)

- 【テーマ1】三角関数のかけ算と無線工学 (第20話) ループフィルタとPLLの応答特性の話(その5)

- 【テーマ1】三角関数のかけ算と無線工学 (第19話) ループフィルタとPLLの応答特性の話(その4)

- 【テーマ1】三角関数のかけ算と無線工学 (第18話) ループフィルタとPLLの応答特性の話(その3)

- 【テーマ1】三角関数のかけ算と無線工学 (第17話) ループフィルタとPLLの応答特性の話(その2)

- 【テーマ1】三角関数のかけ算と無線工学 (第16話) ループフィルタとPLLの応答特性の話(その1)

- 【テーマ1】三角関数のかけ算と無線工学 (第15話) 位相検波器の話

- 【テーマ1】三角関数のかけ算と無線工学 (第14話) PLLの動作原理と代表構成

- 【テーマ1】三角関数のかけ算と無線工学 (第13話) PLLの役割とサイン波の純度について

- 【テーマ1】三角関数のかけ算と無線工学 (第12話) 同一周波数のサイン波のかけ算と位相のはなし

- 【テーマ1】三角関数のかけ算と無線工学 (第11話) ギルバートセル乗算器(その3・ギルバートセル乗算回路)

- 【テーマ1】三角関数のかけ算と無線工学 (第10話) ギルバートセル乗算器(その2・定電流源とカレントミラー回路)

- 【テーマ1】三角関数のかけ算と無線工学 (第9話) ギルバートセル乗算器(その1・差動増幅の基礎)

- 【テーマ1】三角関数のかけ算と無線工学 (第8話) ダブルバランスドミキサ②

- 【テーマ1】三角関数のかけ算と無線工学 (第7話) ダブルバランスドミキサ①

- 【テーマ1】三角関数のかけ算と無線工学 (第6話) トランジスタミキサ②

- 【テーマ1】三角関数のかけ算と無線工学 (第5話) トランジスタミキサ①

- 【テーマ1】三角関数のかけ算と無線工学 (第4話) 非線形動作を利用したかけ算のまとめ

- 【テーマ1】三角関数のかけ算と無線工学 (第3話) ミキサの線形性って何?

- 【テーマ1】三角関数のかけ算と無線工学 (第2話) 周波数変換とミキサ(混合)回路

- 【テーマ1】三角関数のかけ算と無線工学 (第1話) サイン波のかけ算

外部リンク

アマチュア無線関連機関/団体

各総合通信局/総合通信事務所

アマチュア無線機器メーカー(JAIA会員)