今更聞けない無線と回路設計の話

【テーマ2】デシベルと無線工学

第19話 レベルダイヤグラムの縦軸(その3)

2026年5月1日掲載

第19話は、第18話に続きアナログ・デジタル変換(AD変換)の原理と、AD変換の前後におけるレベルダイヤグラムの縦軸(アナログ電圧[dBµV]目盛とデジタル振幅[dBFS]目盛)の関係ついて解説します。

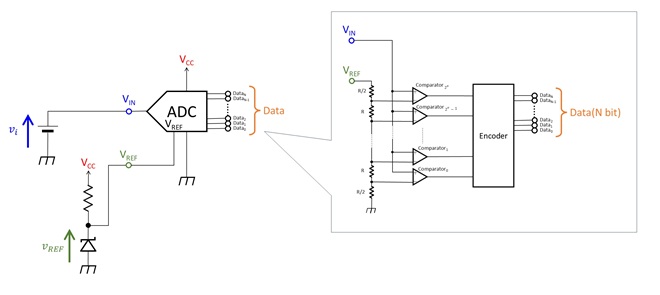

1. ADコンバータ(ADC)の動作原理

ADコンバータ(ADC)は、入力電圧をデジタル(バイナリ)コードに変換するデバイスです。その仕組みは多数の電圧コンパレータで一度に電圧を観測するフラッシュ型や、既知の「のこぎり波」電圧と比較して電圧が一致するまでの時間をカウントするもの、VCOを用いて周波数として検出するものなど、様々な方式が存在します。数MHz~数GHzでのサンプリングが必要な無線通信信号のデジタルサンプリングにおいては、もっぱら図1に示すようなフラッシュ型(並列比較型)もしくはこれに準じた方式のADCが主流です。このタイプのADCでは、出力ビット数をNとすると、2N個の電圧コンパレータを並列に接続し、2N段に等差分圧された基準電圧と比較して、得られた出力をNビットのバイナリコードにエンコードして出力します。最も高速サンプリングが要求される用途では2N個の比較回路と基準電圧を準備しますが、動作速度に余裕がある場合は、入力電圧をサンプリング&ホールドし、比較用の基準電圧を切り替え、あるいはDAコンバータ(DAC)で生成することによって逐次比較を行って回路規模を小さくする工夫がとられます。

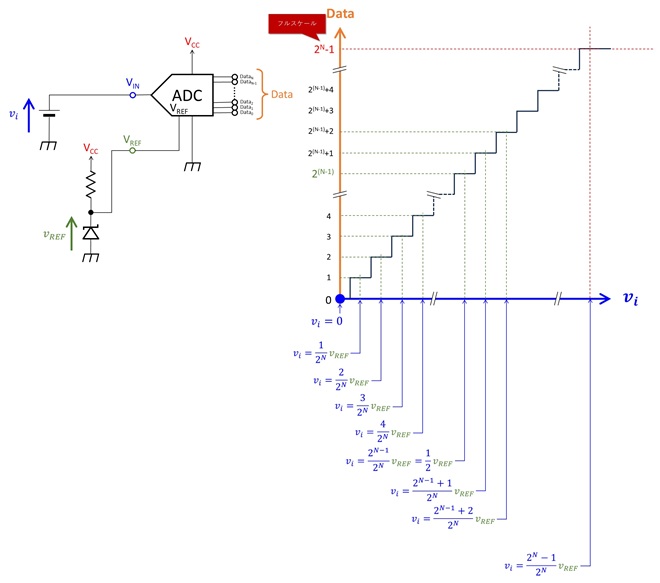

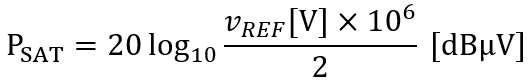

このようにADCは入力電圧を基準電圧と比較することでデジタル符号に変換するデバイスなので、入力電圧端子VINと基準電圧端子VREFの2つのアナログ入力端子が必ずあります。VREF端子に印加される電圧を![]() [V]、アナログ電圧入力端子VINに印加される電圧を

[V]、アナログ電圧入力端子VINに印加される電圧を![]() [V]とすると図2に示すように、

[V]とすると図2に示すように、![]() =0Vの時に0、

=0Vの時に0、 ※1の時にフルスケールのデジタルコードを出力する仕様になっています。通常VREFには低雑音で高安定の電圧源が要求されるため、デバイスに内蔵されたバンドギャップ電圧源、またはこれに準じたシャントレギュレータなどが用いられます。

※1の時にフルスケールのデジタルコードを出力する仕様になっています。通常VREFには低雑音で高安定の電圧源が要求されるため、デバイスに内蔵されたバンドギャップ電圧源、またはこれに準じたシャントレギュレータなどが用いられます。

2. ADコンバータの入力振幅と出力データの関係

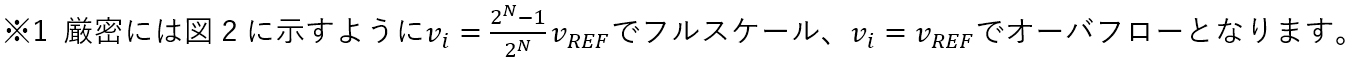

このようにNビットのADCは本質的に0~VREF[V]の入力電圧を0~2N−1のバイナリコードに変換するデバイスです。“マイナス”の入力電圧には直接対応しないため、一般的なシングルエンド入力のADCで交流信号をデジタル化するためには、図3に示すように入力信号にDCバイアスを加える必要があります。

図3 シングルエンド入力タイプのADCによる交流信号のサンプリング

この方法で交流信号をサンプリングすると、ADCの出力にはDCバイアスが重畳された交流信号のバイナリコードが出力されるので、ここからDCバイアス分を引き算して交流成分だけを取り出す処理が必要になります。具体的には、ADCのビット数をNとすると、図3に示すようにバイアス電圧をvREFの1/2の電圧とし、サンプリングデータから2N−1を固定的に引き算するのが一般的です。

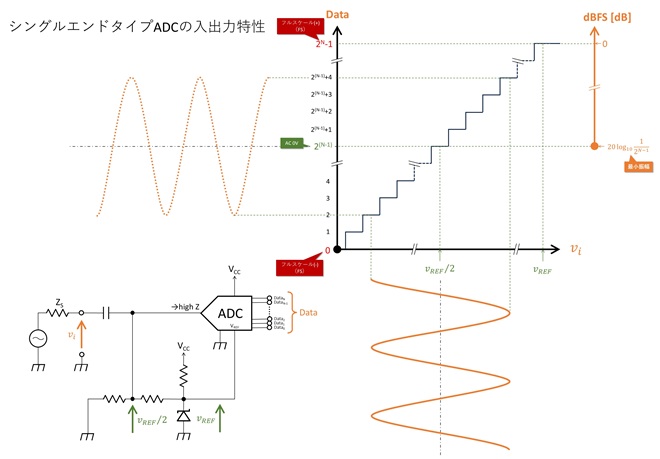

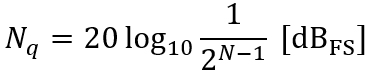

このときADCが扱える最大振幅は![]() [Vp-p]、電圧最大値は

[Vp-p]、電圧最大値は![]() ⁄⁄ 2[VPEAK]、レベルダイヤグラム上においては、信号レベルは電力の次元で扱うので、電圧最大値の2乗を“等価”飽和レベルPSATとして扱い、

⁄⁄ 2[VPEAK]、レベルダイヤグラム上においては、信号レベルは電力の次元で扱うので、電圧最大値の2乗を“等価”飽和レベルPSATとして扱い、

(式2-1)

そして、このレベルが入力されたときの出力値を0[dBFS]、量子化雑音レベルNqは

(式2-2)

となります。

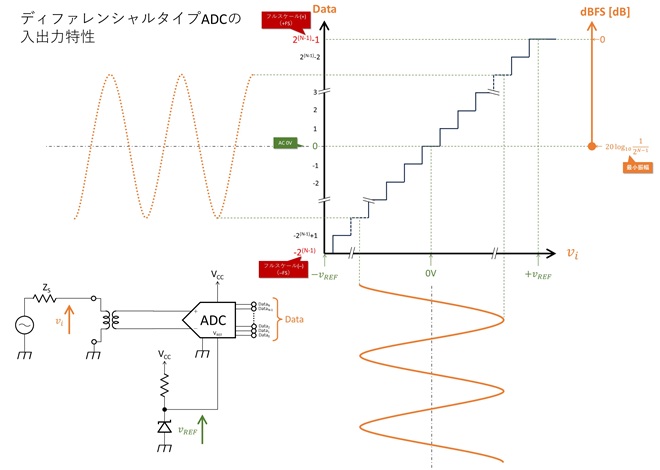

シングルエンド入力タイプのADCでは、バイアス回路の精度が不十分でVREFを正確に1/2に分圧出来ていなかったりすると、直流バイアス相当分の値を引き算したときにオフセットエラーの原因になります。このような外部バイアス回路に伴う不正確さを回避してSNRを改善する目的で、図4~図5に示すような差動入力端子を備えた交流信号に特化したともいえるADCも増えています。

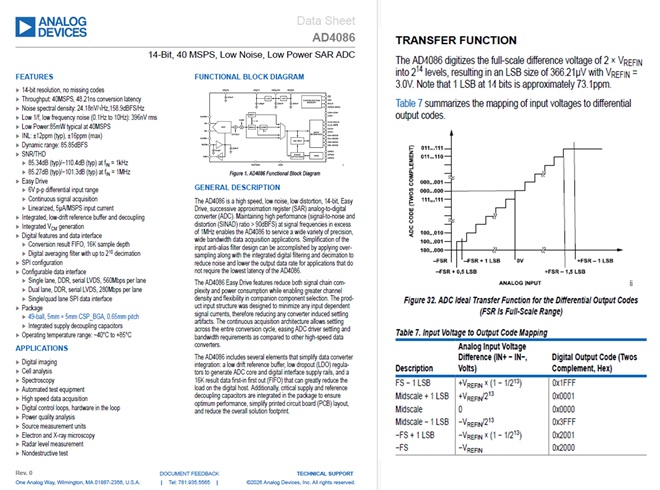

図5 差動入力タイプのADCの例(アナログデバイセズ AD4086)

差動入力タイプのADCでは入力信号の最大振幅が±![]() となり、シングルエンドタイプの2倍の振幅になります。この結果SNRの改善が期待できます。また外付けのバイアス回路は不要で回路設計者がDCオフセット誤差を気にする必要がなくなります。差動入力タイプのADCを採用する場合、シングルエンドタイプのADCと比較して、入力電圧とデジタルデータの関係が6dBずれることになりますので、レベルダイヤグラムを作成する場合は留意する必要があります。

となり、シングルエンドタイプの2倍の振幅になります。この結果SNRの改善が期待できます。また外付けのバイアス回路は不要で回路設計者がDCオフセット誤差を気にする必要がなくなります。差動入力タイプのADCを採用する場合、シングルエンドタイプのADCと比較して、入力電圧とデジタルデータの関係が6dBずれることになりますので、レベルダイヤグラムを作成する場合は留意する必要があります。

次ページは「実際のレベルダイヤグラムを見る」から

今更聞けない無線と回路設計の話 バックナンバー

- 【テーマ2】デシベルと無線工学 (第19話) レベルダイヤグラムの縦軸(その3)

- 【テーマ2】デシベルと無線工学 (第18話) レベルダイヤグラムの縦軸(その2)

- 【テーマ2】デシベルと無線工学 (第17話) レベルダイヤグラムの縦軸(その1)

- 【テーマ2】デシベルと無線工学 (第16話) レベルダイヤグラムの構成

- 【テーマ2】デシベルと無線工学 (第15話) 非線形歪み(その5)

- 【テーマ2】デシベルと無線工学 (第14話) 非線形歪み(その4)

- 【テーマ2】デシベルと無線工学 (第13話) 非線形歪み(その3)

- 【テーマ2】デシベルと無線工学 (第12話) 非線形歪み(その2)

- 【テーマ2】デシベルと無線工学 (第11話) 非線形歪み(その1)

- 【テーマ2】デシベルと無線工学 (第10話) 線形歪み(フェージング現象)

- 【テーマ2】デシベルと無線工学 (第9話) 足される雑音と掛けられる雑音

- 【テーマ2】デシベルと無線工学 (第8話) 等価雑音の内訳

- 【テーマ2】デシベルと無線工学 (第7話) 無線通信の成立条件(その3)

- 【テーマ2】デシベルと無線工学 (第6話) 無線通信の成立条件(その2)

- 【テーマ2】デシベルと無線工学 (第5話) 無線通信の成立条件

- 【テーマ2】デシベルと無線工学 (第4話) dBmとdBµVの複雑な関係

- 【テーマ2】デシベルと無線工学 (第3話) dB(デシベル)を知る(その2)

- 【テーマ2】デシベルと無線工学 (第2話) dB(デシベル)を知る(その1)

- 【テーマ2】デシベルと無線工学 (第1話) (プロローグ)無線通信機の天井と床

- 【テーマ1】三角関数のかけ算と無線工学 (第30話) 三角関数のかけ算と無線工学の切っても切れない深い縁

- 【テーマ1】三角関数のかけ算と無線工学 (第29話) 交流ベクトル空間と直交ミキサ(その4)

- 【テーマ1】三角関数のかけ算と無線工学 (第28話) 交流ベクトル空間と直交ミキサ(その3)

- 【テーマ1】三角関数のかけ算と無線工学 (第27話) 交流ベクトル空間と直交ミキサ(その2)

- 【テーマ1】三角関数のかけ算と無線工学 (第26話) 交流ベクトル空間と直交ミキサ

- 【テーマ1】三角関数のかけ算と無線工学 (第25話) マイナスの周波数

- 【テーマ1】三角関数のかけ算と無線工学 (第24話) 同一周波数のサイン波の掛け算と周波数の話(その3)

- 【テーマ1】三角関数のかけ算と無線工学 (第23話) 同一周波数のサイン波の掛け算と周波数の話(その2)

- 【テーマ1】三角関数のかけ算と無線工学 (第22話) 同一周波数のサイン波の掛け算と周波数の話(その1)

- 【テーマ1】三角関数のかけ算と無線工学 (第21話) ループフィルタとPLLの応答特性の話(その6)

- 【テーマ1】三角関数のかけ算と無線工学 (第20話) ループフィルタとPLLの応答特性の話(その5)

- 【テーマ1】三角関数のかけ算と無線工学 (第19話) ループフィルタとPLLの応答特性の話(その4)

- 【テーマ1】三角関数のかけ算と無線工学 (第18話) ループフィルタとPLLの応答特性の話(その3)

- 【テーマ1】三角関数のかけ算と無線工学 (第17話) ループフィルタとPLLの応答特性の話(その2)

- 【テーマ1】三角関数のかけ算と無線工学 (第16話) ループフィルタとPLLの応答特性の話(その1)

- 【テーマ1】三角関数のかけ算と無線工学 (第15話) 位相検波器の話

- 【テーマ1】三角関数のかけ算と無線工学 (第14話) PLLの動作原理と代表構成

- 【テーマ1】三角関数のかけ算と無線工学 (第13話) PLLの役割とサイン波の純度について

- 【テーマ1】三角関数のかけ算と無線工学 (第12話) 同一周波数のサイン波のかけ算と位相のはなし

- 【テーマ1】三角関数のかけ算と無線工学 (第11話) ギルバートセル乗算器(その3・ギルバートセル乗算回路)

- 【テーマ1】三角関数のかけ算と無線工学 (第10話) ギルバートセル乗算器(その2・定電流源とカレントミラー回路)

- 【テーマ1】三角関数のかけ算と無線工学 (第9話) ギルバートセル乗算器(その1・差動増幅の基礎)

- 【テーマ1】三角関数のかけ算と無線工学 (第8話) ダブルバランスドミキサ②

- 【テーマ1】三角関数のかけ算と無線工学 (第7話) ダブルバランスドミキサ①

- 【テーマ1】三角関数のかけ算と無線工学 (第6話) トランジスタミキサ②

- 【テーマ1】三角関数のかけ算と無線工学 (第5話) トランジスタミキサ①

- 【テーマ1】三角関数のかけ算と無線工学 (第4話) 非線形動作を利用したかけ算のまとめ

- 【テーマ1】三角関数のかけ算と無線工学 (第3話) ミキサの線形性って何?

- 【テーマ1】三角関数のかけ算と無線工学 (第2話) 周波数変換とミキサ(混合)回路

- 【テーマ1】三角関数のかけ算と無線工学 (第1話) サイン波のかけ算

外部リンク

アマチュア無線関連機関/団体

各総合通信局/総合通信事務所

アマチュア無線機器メーカー(JAIA会員)